跨时钟域的典型:异步FIFO的设计

跨时钟域的典型范例——异步FIFO

“时钟域(clock domain)”可以说是数字集成电路中一个非常重要的内容了,那么,何谓“跨时钟域”?

很好理解,在时序逻辑电路中,所有触发器、寄存器的运行都是由时钟激励而运行下去的。而一个大型的数字系统中不可能只有一种时钟:

例如Cortex-M3软核常常运行在50~100MHz、而UART串行口波特率要在921600以上的话,输入时钟频率最好高于200MHz、FPGA上的DDR3一般要求200MHz的时钟输入,不同PLL/MMCM输出的同频率时钟它们的相位也有可能不同……

这么多不同时钟激励的系统要组合在一起并能进行数据交互,那么势必会遇到“跨时钟域”的问题,解决这个问题的一大方法之一就是利用异步FIFO进行数据交互

¶什么是FIFO

FIFO(First In First Out),顾名思义,即先输入先输出的一种模块,FIFO一般分为同步FIFO和异步FIFO两种,同步FIFO即输入和输出在同一个时钟域中,异步FIFO即输入输出不处于同一个时钟域。

FIFO的存储模块可以看成一个二维寄存器(当然也可以通过生成ram代替),因此有些概念需要掌握,即:

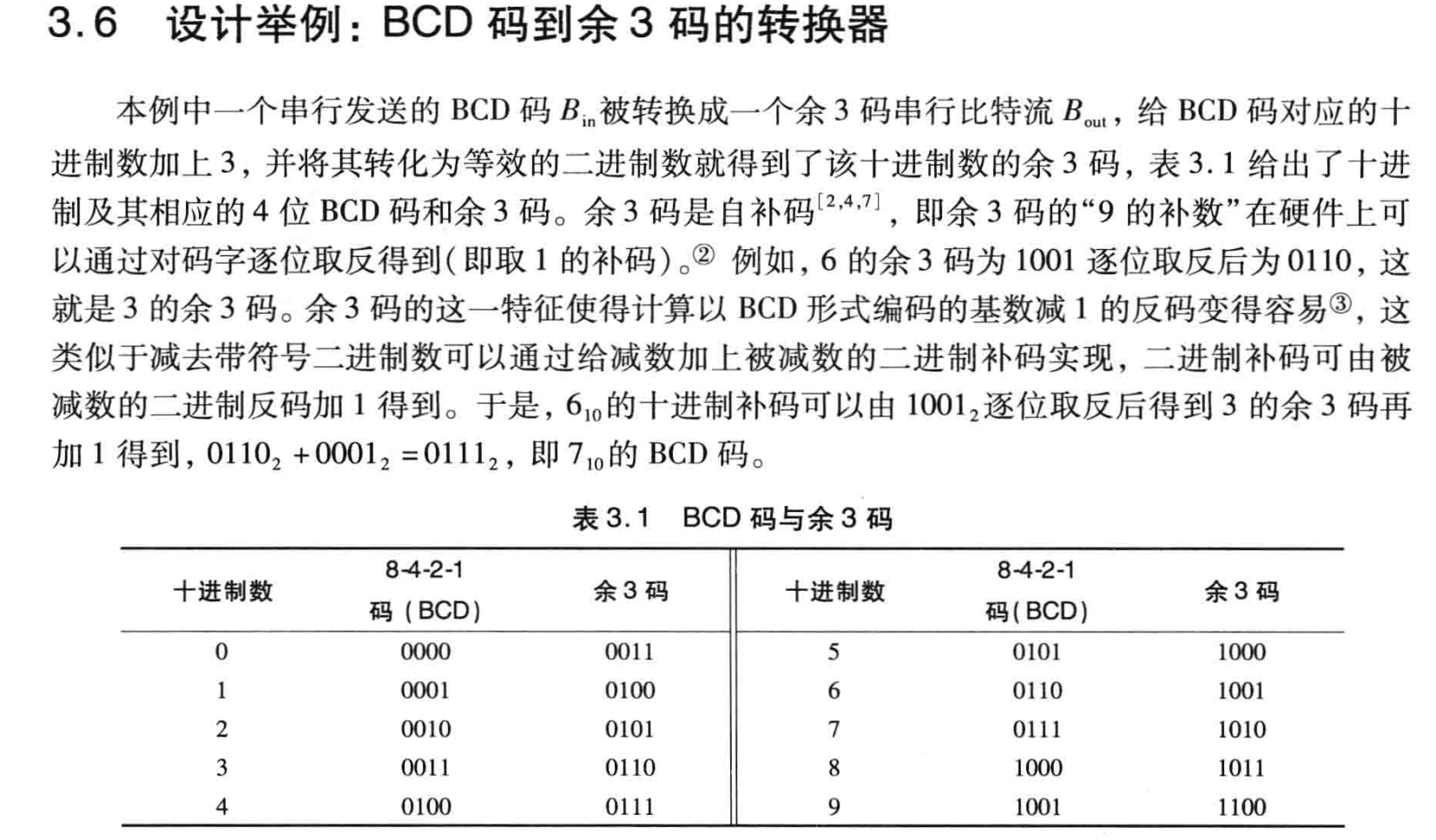

说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅

说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅